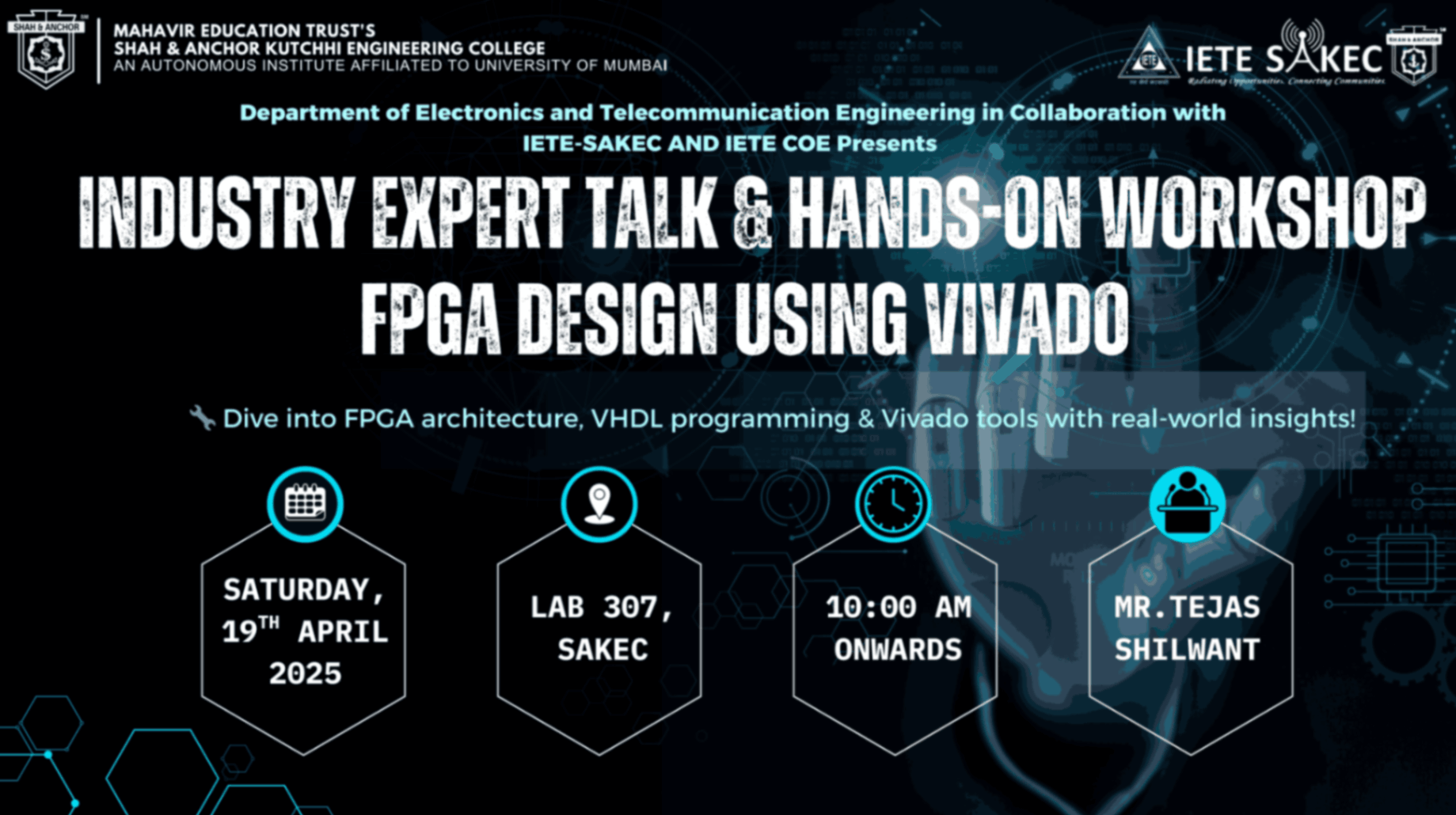

Title: Industry Expert Talk and Hands-On Workshop on “FPGA Design using Vivado”

Organized by: EXTC Department, SAKEC in collaboration with IETE-SAKEC and IETE COE

Date: Saturday, 19th April 2025

Time: 10:00 AM onwards

Venue: Lab 307, SAKEC

Resource Person: Mr. Tejas Shilwant, FPGA Design Engineer, Paras Anti-Drone Technologies Pvt Ltd

Special Guest: Mr. Sarvan Tejas, Junior Engineer, Paras Anti-Drone Technologies Pvt Ltd

Total Participants: 42

Faculty coordinators: Ms Shwetha Shetty and Dr. Anusaka Gon, SAKEC

Objective of the Workshop:

To provide students with hands-on exposure to FPGA design principles using Vivado, and to bridge the gap between academic concepts and industry practices in digital system design.

Session Highlights:

- Inauguration and Welcome

- Expert Talk by Mr. Tejas Shilwant

- Guidelines on Choosing an FPGA

- Detailed Overview of Artix-7 FPGA

- Interactive Q&A and Project Discussion Session

- Hands-On Demonstration Session

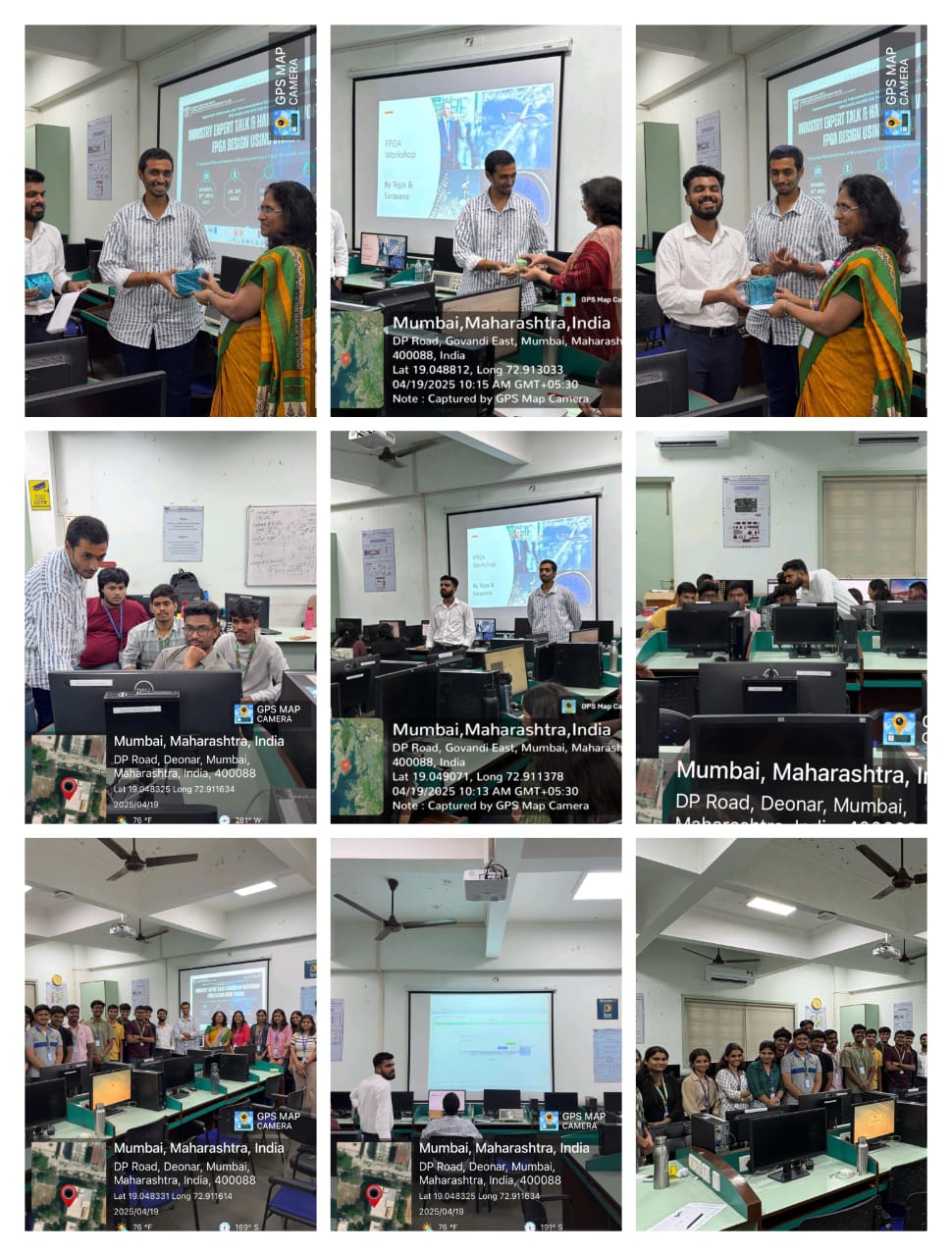

The EXTC Department of SAKEC, in collaboration with IETE-SAKEC and under the banner of the IETE Centre of Excellence, successfully organized an Industry Expert Talk and Hands-On Workshop on “FPGA Design using Vivado” on Saturday, 19th April 2025, at Lab 307. The session was conducted by Mr. Tejas Shilwant, an FPGA Design Engineer at Paras Anti-Drone Technologies, accompanied by Junior Engineer Mr. Sarvan Tejas. The event aimed to bridge the gap between academic learning and industry expectations by introducing students to the practical aspects of FPGA architecture and design.

Mr. Tejas began the session with an engaging talk on the significance of FPGAs in today’s rapidly evolving tech landscape, particularly in defense and embedded systems. He shared his industry experience and provided a detailed walkthrough of the FPGA design flow using the Vivado Design Suite, emphasizing the relevance of VHDL for designing synthesizable digital systems. A key highlight of the session was the discussion on how to choose an appropriate FPGA, where students were guided through essential parameters such as logic resources, speed, power consumption, and toolchain compatibility. In this context, the Xilinx Artix-7 FPGA was introduced in detail, showcasing its features such as low power consumption, integrated DSP slices, block RAMs, and its suitability for both academic and industrial applications.

The session also included a valuable hands-on demonstration in which participants observed the process of designing and implementing block RAM (BRAM) using IP (Intellectual Property) in Vivado. Students learned how to create and instantiate BRAM components, simulate their behavior, and understand data read/write operations in VHDL. Following this, an interactive discussion took place where students enthusiastically posed questions, discussed their ongoing and future projects, and explored how FPGA could enhance their applications in areas like signal processing, sensor interfacing, and embedded system development.

The event saw active participation and positive feedback from students, who found the session highly informative and motivating. The blend of technical insight and practical demonstration encouraged many to consider FPGA design for their final-year projects. The event was also promoted on SAKEC’s and IETE-SAKEC’s official social media platforms, further amplifying its reach and impact. Overall, the workshop proved to be a valuable learning experience, fostering curiosity and innovation among the participants

The workshop successfully introduced participants to the world of FPGA design using Vivado. It bridged theoretical concepts with practical exposure, igniting curiosity and technical confidence among students to explore programmable logic in real-world applications.